# **AMC541**

# Xilinx Zynq UltraScale+ FPGA with TCI6638 Multicore DSP+ARM, AMC

**AMC541**

# **Key Features**

- Xilinx Zynq®UltraScale+™ XCZU19EG FPGA Multi Processor System on Chip (MPSoC)

- TCI6638K2K Multicore DSP+ARM® KeyStone II System-on-Chip (SoC)

- Dual bank of DDR-4 64-bit wide with ECC to FPGA/SOC (16 GB total)

- Dual banks of DDR3 64-bit wide with ECC to TCl6638 (16 GB total)

- 3 SFP+ connectors to the front panel

- PCIe (AMC.1), 10/40GbE (AMC.2), SRIO (AMC.4) capability on ports 4-7 (x4) and 8-11 (x4) per FPGA load

- SRIO x4 to DSP via MUX selection

- GbE on ports 0,1 (AMC.2)

## **Benefits**

- MPSoC FPGA and SoC DSP+ARM combination provides dense signal processing

- Electrical, mechanical, software, and system-level expertise in house

- Full system supply from industry leader

- AS9100 and ISO9001 certified company

## **AMC541**

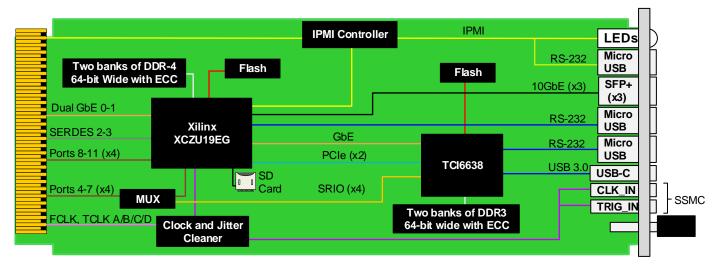

The AMC541 is based on Xilinx Zynq Ultrascale+ XCZU19EG MPSoC FPGA with embedded Quad-core ARM Cortex-A53 application processing unit, Dual-core ARM Cortex-R5 real-time processing unit, ARM Mali - MP2 GPU. The FPGA has Dual banks of 64-bit DDR4 memory (one bank to the ARM Core and one bank to the FPGA) and includes an SD card.

The AMC541 has the TCl6638K2K communications infrastructure KeyStone SoC which is a member of the C66x family based on Tl's new KeyStone II Multicore SoC Architecture designed specifically for high-performance telecommunication, IoT and networking applications. It features eight TMS320C66x DSP core subsystems (C66x CorePacs). The TMS320C66x interfaces to dual 64-bit wide DRAM DDR-3.

The flexible architecture including multiplexer allows the FPGA and DSP to interface to the AMC connector in different configurations. The AMC connector ports 2-3 and 8-11 are linked directly to the FPGA for the core to interface with the host through multiple protocols such as SRIO, PCle or 10/40GbE. The Ports 4-7 can connect directly to the FPGA in addition to Ports 8-11 or connect directly to the DSP with SRIO protocol via MUX selection (DIP-switch selection).

The module also routes GbE on Ports 0 and 1 per AMC.2. The DSP and FPGA are linked via PCle x2 and GbE.

The on-board, re-configurable FPGA interfaces to the AMC FCLKA (fabric clock) and TCLKA-D (user clocks and triggers) via a clock and jitter cleaner. The module also has a front panel TRIG IN and CLK IN to the clock and jitter cleaner.

The front panel SFP+ cage allow expansion via fiber 1/10GbE or 1/10GbE copper interface.

Figure 1: AMC541

# **Block Diagram**

Figure 2: AMC541 Functional Block Diagram

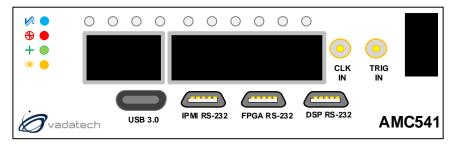

## **Front Panel**

Figure 3: AMC541 Front Panel

# **Specifications**

| A . I . Y Y              |                                                                           |                                                                             |  |

|--------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| Architecture             |                                                                           |                                                                             |  |

| Physical                 | Dimensions                                                                | Single module, full-size                                                    |  |

|                          |                                                                           | Width: 2.89" (73.5 mm)                                                      |  |

|                          |                                                                           | Depth 7.11" (180.6 mm)                                                      |  |

| Туре                     | FPGA MPSoC AMC                                                            | Xilinx Zynq® UltraScale+™ XCZU19EG                                          |  |

|                          | DSP+ARM SoC                                                               | TCl6638K2KCXAAWA2(4); security accelerator enabled / general-purpose device |  |

| Standards                |                                                                           |                                                                             |  |

| AMC                      | Туре                                                                      | AMC.0, AMC.1, AMC.2 and AMC.4                                               |  |

| <b>Module Management</b> | IPMI                                                                      | IPMI v2.0                                                                   |  |

| PCle                     | Lanes                                                                     | x4 or x8 (ports 4-11), additional ports on 2-3                              |  |

| SRIO                     | Lanes                                                                     | Dual x4 (ports 4-11), additional ports on 2-3                               |  |

| 10/40 GbE                | Lanes                                                                     | Dual x4 (ports 4-11), additional ports on 2-3                               |  |

| SRIO                     | Lanes                                                                     | Single x4 to DSP (ports 4-7)                                                |  |

| Configuration            |                                                                           |                                                                             |  |

| Power                    | AMC541                                                                    | 60 W (application specific)                                                 |  |

| Environmental            | Temperature                                                               | See ordering options and environmental spec sheet                           |  |

|                          |                                                                           | Storage Temperature: -40° to +85°C                                          |  |

|                          | Vibration                                                                 | Operating 9.8 m/s <sup>2</sup> (1 G), 5 to 500 Hz on each axis              |  |

|                          |                                                                           | Operating 30 Gs on each axis                                                |  |

|                          | Relative Humidity                                                         | 5 to 95% non-condensing                                                     |  |

| Front Panel              | Interface Connectors                                                      | · · · · · · · · · · · · · · · · · · ·                                       |  |

|                          |                                                                           | IPMI, FPGA and DSP serial RS-232 via Micro USB (2.0)                        |  |

|                          |                                                                           | USB Type C (3.0)                                                            |  |

|                          |                                                                           | Clk In and Trigger In via SSMC                                              |  |

|                          | LEDs                                                                      | IPMI management control                                                     |  |

|                          |                                                                           | Status                                                                      |  |

|                          | Mechanical                                                                | Hot swap ejector handle                                                     |  |

| Software Support         | Operating System                                                          | · ·                                                                         |  |

| Other                    |                                                                           |                                                                             |  |

| MTBF                     | MIL Hand book 217-F@ TBD hrs                                              |                                                                             |  |

| Certifications           | Designed to meet FCC, CE and UL certifications, where applicable          |                                                                             |  |

| Standards                | VadaTech is certified to both the ISO9001:2000 and AS9100B:2004 standards |                                                                             |  |

| Warranty                 | Two (2) years                                                             |                                                                             |  |

| -                        | . , ,                                                                     |                                                                             |  |

#### INTEGRATION SERVICES AND APPLICATION-READY PLATFORMS

VadaTech has a full ecosystem of OpenVPX, ATCA and MTCA products including chassis platforms, shelf managers, AMC modules, Switch and Payload Boards, Rear Transition Modules (RTMs), Power Modules, and more. The company also offers integration services as well as preconfigured Application-Ready Platforms. Please contact VadaTech Sales for more information.

## **Ordering Options**

#### AMC541 - ABC-DEF-GHJ

| A = DSP Model                                                                                           | D = PCle Option                                                                                  | G = SFP+ 10GbE base-SR (***)                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 = TCI6638K2KCXAAWA2<br>1 = TCI6638K2KCXAAWA24                                                         | 0 = No PCIe<br>1 = PCIe on ports 4-7 (*)<br>2 = PCIe on ports 8-11<br>3 = PCIe on ports 4-11 (*) | 0 = No SFP+10GbE base-SR<br>1 = 1<br>2 = 2<br>3 = 3                                                                                                                                                                                                                                                                                                                                                                                   |

| B = Clock                                                                                               | E = DSP SRIO                                                                                     | H = SFP Copper 1000Base-T (***)                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0 = Standard (XO)<br>1 = Stratum-3 (TCXO)                                                               | 0 = No DSP SRIO<br>1 = DSP SRIO to Ports 4-7*                                                    | 0 = No SFP Copper 1000Base-T<br>1 = 1<br>2 = 2<br>3 = 3                                                                                                                                                                                                                                                                                                                                                                               |

| C = Front Panel                                                                                         | F = SFP+ 10GbE Copper (***)                                                                      | J = Temperature Range and Coating                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 = Reserved 2 = Reserved 3 = Full-size 4 = Reserved 5 = Reserved 6 = Full-size, MTCA.1 (captive screw) | 0 = No SFP+ 10GbE Copper<br>1 = 1<br>2 = 2<br>3 = 3                                              | 0 = Commercial (-5° to +55°C), No coating 1 = Commercial (-5° to +55°C), Humiseal 1A33 Polyurethane 2 = Commercial (-5° to +55°C), Humiseal 1B31 Acrylic 3 = Industrial (-20° to +70°C), No coating 4 = Industrial (-20° to +70°C), Humiseal 1A33 Polyurethane 5 = Industrial (-20° to +70°C), Humiseal 1B31 Acrylic 6 = Extended (-40° to +85°C), Humiseal 1A33 Polyurethane** 7 = Extended (-40° to +85°C), Humiseal 1B31 Acrylic** |

Notes: \*Only D=0 and D=2 are compatible with E=1

## **Related Products**

VT815

I ITCOOA

- Intel® Xeon E3 processor options with PCH

- DVI graphics (SM750 w/16 MB DDR), up to 1920x1440 resolution

- Optional up to 256 GB SSD with RAID option

- 9U MTCA Chassis Platform, 12 slot, double-module

- Full redundancy

- High-bandwidth (20-lane) connections between adjacent slots

- Single module, full size per AMC.0

- Unified 1 GHz quad-core CPU for MCMC (MicroTCA Carrier Management Controller) Shelf Manager, Clocking, and Fabric management

- Automatic fail-over with redundant UTC004s

<sup>\*\*</sup>Conduction cooled, temperature is at edge of module. Consult factory for availability

<sup>\*\*\*</sup>F + G + H = 3 maximum

## **Contact**

VadaTech Corporate Office

198 N. Gibson Road, Henderson, NV 89014 Phone: +1 702 896-3337 | Fax: +1 702 896-0332

Asia Pacific Sales Office

7 Floor, No. 2, Wenhu Street, Neihu District, Taipei 114, Taiwan Phone: +886-2-2627-7655 | Fax: +886-2-2627-7792

VadaTech European Sales Office

VadaTech House, Bulls Copse Road, Southampton, SO40 9LR Phone: +44 2380 016403

info@vadatech.com | www.vadatech.com

## Choose VadaTech

#### We are technology leaders

- First-to-market silicon

- Constant innovation

- · Open systems expertise

#### We commit to our customers

- · Partnerships power innovation

- · Collaborative approach

- · Mutual success

#### We deliver complexity

- · Complete signal chain

- · System management

- · Configurable solutions

#### We manufacture in-house

- · Agile production

- · Accelerated deployment

- AS9100 accredited

#### **Trademarks and Disclaimer**

The VadaTech logo is a registered trademark of VadaTech, Inc. Other registered trademarks are the property of their respective owners.

AdvancedTCA™ and the AdvancedMC™ logo are trademarks of the PCI Industrial Computers Manufacturers Group. All rights reserved.

Specification subject to change without notice.