# XMC-VLX User-Configurable Virtex-5 FPGA Modules with Plug-In I/O

**24** HR Stock Item

XMC module with PCIe interface ◆ Logic-optimized Virtex-5 FPGA ◆ I/O extension mezzanine modules

# **Description**

## Models

XMC-VLX85: 85k logic cells XMC-VLX110: 110k logic cells XMC-VLX155: 155k logic cells

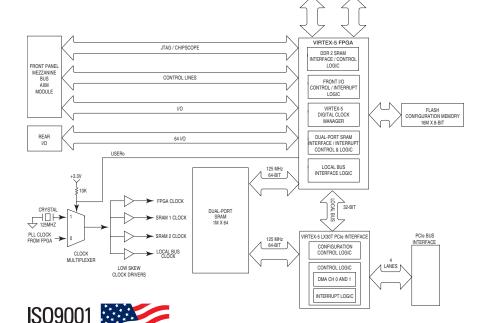

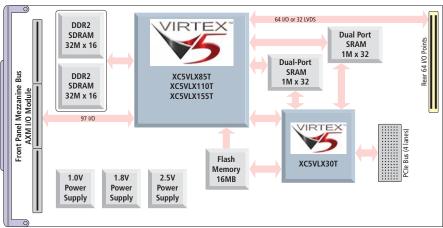

Acromag's XMC-VLX mezzanine modules feature a configurable Xilinx® Virtex™-5 FPGA enhanced with multiple high-speed memory buffers and a high-throughput PCIe interface. Field I/O interfaces to the FPGA via the rear J4/P4 connector and/or with optional front mezzanine plug-in I/O modules. The result is a powerful and flexible I/O processor module that is capable of executing your custom instruction sets and algorithms.

Three models provide a choice of logic-optimized FPGAs to match your performance requirements. Although there is no limit to the uses for these boards, several applications are ideal. Typical uses include hardware simulation, military servers, communications, in-circuit diagnostics, signal intelligence, and image processing.

64 I/O lines are accessible through the rear (J4) connector. Additional I/O processing is supported on a separate mezzanine card that plugs into the FPGA base board. A variety of these external I/O cards are available to interface for your analog and digital I/O signals.

Large, high-speed memory banks provide efficient data handling. Generous DDR2 SDRAM buffers store captured data prior to FPGA processing. Afterward, data is moved to dual-port SRAM for high-speed DMA transfer to the bus or CPU. Our high-bandwidth PCIe interface ensures fast data throughput.

Take advantage of the conduction-cooled design for use in hostile environments. Conduction efficiently dissipates heat if there is inadequate cooling air flow. Optional extended temperature models operate reliably from -40 to 85°C.

Acromag's Engineering Design Kit provides software utilities and example VHDL code to simplify your program development and get you running quickly. A JTAG interface enables on-board VHDL debugging.

Plug in an AXM analog or digital I/O module for additional I/O signal processing capabilities.

# **Key Features & Benefits**

- Reconfigurable Xilinx Virtex-5 FPGA

- PCIe bus 4-lane Gen 1 interface

- Supports both front and rear I/O connections

- 64 I/O or 32 LVDS lines direct to FPGA via rear (J4) connector

- Plug-in I/O extension modules are available for the front mezzanine

- FPGA code loads from the PCIe bus or from flash memory

- 1M x 64-bit dual-ported SRAM provides direct links from the PCIe bus and to the FPGA

- 32M x 32-bit DDR2 SDRAM is directly accessed through the FPGA

- Other memory options available (call factory)

- Supports dual DMA channel data transfer to the CPU/bus

- Support for Xilinx ChipScope<sup>™</sup> Pro interface

- Designed for conduction-cooled host card or -40 to 85°C operation in air-cooled systems

Tel 248-295-0310 ■ Fax 248-624-9234 ■ solutions@acromag.com ■ www.acromag.com ■ 30765 Wixom Rd, Wixom, MI 48393 USA

# XMC-VLX User-Configurable Virtex-5 FPGA Modules with Plug-In I/O

# **Performance Specifications**

### FPGA

### FPGA Device

Xilinx Virtex-5 FPGA.

Model XMC-VLX85:

XC5VLX85T-1FF1136 FPGA with 82,944 logic cells and 48 DSP48E slices.

Model XMC-LX110:

XC5VLX110T-1FF1136 FPGA with 110,592 logic cells and 64 DSP48E slices.

Model XMC-LX155:

XC5VLX155T-1FF1136 FPGA with 155,648 logic cells and 128 DSP48E slices.

### FPGA configuration

Download via PCIe bus or flash memory.

## Example FPGA program

VHDL provided for bus interface, front & rear I/O control, SRAM read/write interface logic, and SDRAM memory interface controller. See EDK kit.

### I/O Processing

Acromag AXM I/O modules:

AXM modules plug into the XMC module's front mezzanine for additional I/O lines. Analog and digital I/O AXM modules are sold separately.

## Rear I/O

AS9100

64 I/O (32 LVDS) lines supported with a direct connection between the FPGA and the rear I/O connector (J4).

# Engineering Design Kit

Provides user with basic information required to develop a custom FPGA program. Kit must be ordered with the first purchase of a XMC-VLX module (see www.acromag.com for more information).

## XMC Compliance

Conforms to PCI Express 1.1a electrical and protocol standards. 2.5Gbps data rate per lane per direction.

Complies with ANSI/VITA 42.0 specification for XMC module mechanicals and connectors.

Complies with ANSI/VITA 42.3 specification for XMC modules with PCI Express interface.

Electrical/Mechanical Interface: Single-Width Module.

### Environmental

Operating temperature

-0 to 70°C or -40 to 85°C (E versions)

## Storage temperature

-55 to 125°C.

### Relative humidity

5 to 95% non-condensing.

### Power

3.3V (±5%): 700mA typical, 840mA maximum +12V (±5%): 820mA typical, 984mA maximum

BATE 2

32M X 16

Contact the factory.

DOUBLE DATA RATE 2 SDRAM

32M X 16

# XMC Modules

**Ordering Information**

XMC-VLX85

User-configurable Virtex-5 FPGA, 85k logic cells

### XMC-VLX85E

Same as XMC-VLX85 with extended temp. range

### XMC-VLX110

User-configurable Virtex-5 FPGA, 110k logic cells

### XMC-VLX110E

Same as XMC-VLX110 with extended temp. range

### XMC-VLX155

User-configurable Virtex-5 FPGA, 155k logic cells

Same as XMC-VLX155 with extended temp. range

### XMC-VLX-EDK

Engineering Design Kit (one kit required)

## ■ AXM Plug-In I/O Extension Modules

For more information, see www.acromag.com.

### AXM-A30

2 analog input 100MHz 16-bit A/D channels

### AXM-D02

30 RS485 differential I/O channels

# AXM-D03

16 CMOS and 22 RS485 differential I/O channels

### AXM-D04

30 LVDS I/O channels

Custom I/O configurations available, call factory.

## Software

For more information, see www.acromag.com.

### PMCSW-API-VXW

VxWorks® software support package

## PCISW-API-QNX

QNX® software support package

### PCISW-API-WIN

Windows® DLL software support package

### PCISW-LINUX

Linux™ support (website download only)